На главную

--------------------------------------------------------------------------------

nedoPC.org

--------------------------------------------------------------------------------

--------------------------------------------------------------------------------

INTEL • Порт компилятора С с8080 в Typescript и онлайн

Я портанул компилятор Морозова c8080 в TypeScript.

По функциональности - это на 100% оригинал на основе всех тестов, что есть в оригинале. Я по ходу нашел один баг в оригинальном токенизаторе у Морозова.

Ассемблер я прикрутил свой asm8, и он у меня встроен прямо в компилятор. Единственное, я расширил форматы выходных файлов, ибо у оригинала только формат .RKS (Специалист).Я прикрутил онлайновый плейграунд - rk86.ru/beta/c8080. Можно налету компилировать и запустить в эмуляторе. В плейграунде только только компилятор, без include'ов. Чисто С.

Для обычной работы с командной строке:илиЕсли нужны разные его include'ы -- пока их надо брать из репозитория родного компилятора. Просто меня лично интересует только РК, а для него никаких include'ов особо не нужно.Statistics: Posted by begoon — 23 Apr 2026 21:04

--------------------------------------------------------------------------------

ZX Spectrum (RUS) • Re: Развиваем Балтик

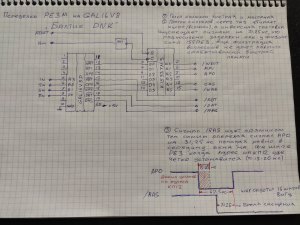

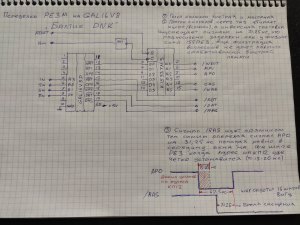

GAL вместо РЕ3М, работает с прямой заменой, прошивку с исключением ЛП8 не пробовал, просто накидал стандартный код, даже резисторы подтяжки не выпаявал, на этих малых частотах работает все стабильно

/* *************** INPUT PINS *********************/

PIN 3=A0 ; /* */

PIN 4=A1 ; /* */

PIN 5=A2 ; /* */

PIN 6=A3 ; /* */

PIN 7=A4 ; /* */

/* *************** OUTPUT PINS *********************/

PIN 12=D0 ; /* */

PIN 13=D1 ; /* */

PIN 14=D2 ; /* */

PIN 15=D3 ; /* */

PIN 16=D4 ; /* */

PIN 17=D5 ; /* */

PIN 18=D6 ; /* */

PIN 19=D7 ; /* */

FIELD ADDR = [A4,A3,A2,A1,A0];

FIELD OUTPUT = [D7,D6,D5,D4,D3,D2,D1,D0];

TABLE ADDR => OUTPUT {

'b'00000000 => 'b'10110100;

'b'00000001 => 'b'10110101;

'b'00000010 => 'b'10110110;

'b'00000011 => 'b'11111111;

'b'00000100 => 'b'10111011;

'b'00000101 => 'b'11001011;

'b'00000110 => 'b'11011011;

'b'00000111 => 'b'11111111;

'b'00001000 => 'b'00111011;

'b'00001001 => 'b'01001011;

'b'00001010 => 'b'01011011;

'b'00001011 => 'b'11111111;

'b'00001100 => 'b'01110100;

'b'00001101 => 'b'01110101;

'b'00001110 => 'b'01110110;

'b'00001111 => 'b'11111111;

'b'00010000 => 'b'10001011;

'b'00010001 => 'b'10011011;

'b'00010010 => 'b'10101011;

'b'00010011 => 'b'11111111;

'b'00010100 => 'b'10001011;

'b'00010101 => 'b'10011011;

'b'00010110 => 'b'10101011;

'b'00010111 => 'b'11111111;

'b'00011000 => 'b'00001011;

'b'00011001 => 'b'00011011;

'b'00011010 => 'b'00101011;

'b'00011011 => 'b'11111111;

'b'00011100 => 'b'01001011;

'b'00011101 => 'b'01011011;

'b'00011110 => 'b'01101011;

'b'00011111 => 'b'11111111;

}Statistics: Posted by DIM — 23 Apr 2026 19:45

--------------------------------------------------------------------------------

ZX Spectrum (RUS) • Re: Развиваем Балтик

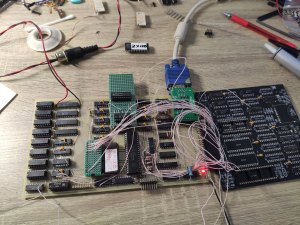

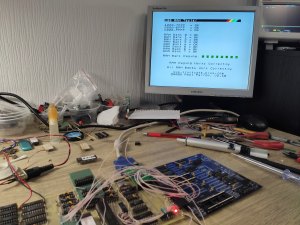

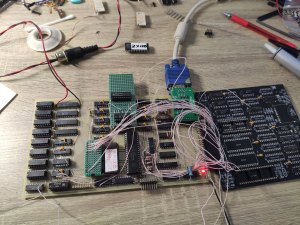

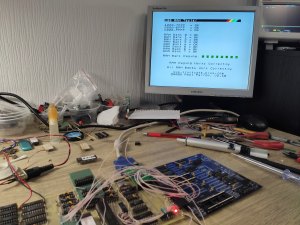

за основу был взят стандартный код прошивки Балтика, построена такая шляпа и не помню сколько десятков часов экспериментов и кодовой писанины с применением логического анализатора, осциллографа родилась рабочая схема для этой памяти.

Внимание!!! РУ5Г, просто РУ5, U2164 C15 с этой схемой работали не стабильно, времени заниматься подбором задержек с помощью конденсаторов у меня не было, мне нужно было запустить 41256 и это я сделал.

/* *************** INPUT PINS *********************/

PIN 5=A3 ; /* */

PIN 6=A2 ; /* */

PIN 7=A1 ; /* */

PIN 8=A0 ; /* */

/* *************** OUTPUT PINS *********************/

PIN 12=D0 ; /* */

PIN 13=D1 ; /* */

PIN 14=D2 ; /* */

PIN 15=D3 ; /* */

PIN 16=D4 ; /* */

PIN 17=D5 ; /* */

PIN 18=D6 ; /* */

PIN 19=D7 ; /* */

FIELD ADDR = [A3,A2,A1,A0];

FIELD OUTPUT = [D7,D6,D5,D4,D3,D2,D1,D0];

TABLE ADDR => OUTPUT {

'b'0000 => 'b'00000101;

'b'0001 => 'b'00010101;

'b'0010 => 'b'00110101;

'b'0011 => 'b'10110101;

'b'0100 => 'b'10110010;

'b'0101 => 'b'10100010;

'b'0110 => 'b'00100110;

'b'0111 => 'b'01110110;

'b'1000 => 'b'01110110;

'b'1001 => 'b'01101110;

'b'1010 => 'b'01101110;

'b'1011 => 'b'01111110;

'b'1100 => 'b'01111110;

'b'1101 => 'b'11111110;

'b'1110 => 'b'11100110;

'b'1111 => 'b'11100001;

}Statistics: Posted by DIM — 23 Apr 2026 19:21

--------------------------------------------------------------------------------

ZX Spectrum (RUS) • Re: Развиваем Балтик

мне нужно было запустить эту память, из 10 штук РЕ3 и цепочки конденсаторов только одна решка может работатьStatistics: Posted by DIM — 23 Apr 2026 19:17

--------------------------------------------------------------------------------

Вебсайт и форумы • Re: На сайте нет httpS и это может стать проблемой

Я пока не понимаю как http может сосуществовать с https - сейчас похоже на то, что если браузер видит, что есть https то он лезет на https, даже если ты явно написал http://Statistics: Posted by Shaos — 23 Apr 2026 18:21

--------------------------------------------------------------------------------

Вебсайт и форумы • Re: На сайте нет httpS и это может стать проблемой

В http тож есть смысл - можно под ХР смотреть. В идеале, хорошо бы сделать так, чтоб логиниться можно было токо под https, а если токо смотреть - то под http. Хорошо, если ретро сайт поддерживает ретро операционки.Statistics: Posted by Black_Cat — 23 Apr 2026 16:39

--------------------------------------------------------------------------------

Программное обеспечение • Re: Кодим с wxWidgets

Наброски чего?

приложения, извините могу выражаться не точно, я плохо знаю русский.

Исходники варианта с PLplot показать не могу т.к. писал за деньги для другой конторы...Statistics: Posted by Shaos — 23 Apr 2026 05:59

--------------------------------------------------------------------------------

Radio-86RK • Re: Полные реверсы игр: Volcano, Лестница, Диверсант, Алмаз (ALIAZ1)

Да можно не гадать. В README.md все написано.Statistics: Posted by begoon — 22 Apr 2026 19:39

--------------------------------------------------------------------------------

Radio-86RK • Re: Полные реверсы игр: Volcano, Лестница, Диверсант, Алмаз (ALIAZ1)

А как насчёт интеллектуальных прав А.Бытко? Просто интересно.)Statistics: Posted by Mondx — 22 Apr 2026 19:32

--------------------------------------------------------------------------------

Radio-86RK • Re: Дизассемблирование игр: Volcano, Лестница, Диверсант, Алмаз (ALIAZ1)

Полный реверс игры Алмаз (ALIAZ1), включая картыЕсли кому интересно -- внутри игры много следов от Микроши, типа запись в D80x, но все как-то недоделано, поэтому точно не ясно: это адаптация из Микроши в РК или наоборот.Statistics: Posted by begoon — 22 Apr 2026 18:33

--------------------------------------------------------------------------------

ZX Spectrum (RUS) • Re: Развиваем Балтик

Хм, интересно - держи в курсе, буду повторять...Statistics: Posted by Shaos — 22 Apr 2026 16:02

--------------------------------------------------------------------------------

Radio-86RK • Re: Дизассемблирование игр Volcano, Лестница и Диверсант

вот рикошет бы ....

но смысла нет, так как он тормознутый, и если его просто реверснуть то он так и останется тормозомStatistics: Posted by imsushka — 22 Apr 2026 15:35

--------------------------------------------------------------------------------

Radio-86RK • Re: Дизассемблирование игр Volcano, Лестница и Диверсант

Запилил очень подробный реверс еще одной моей любимой игрухи - Диверсант.Как обычно, реверс собирается в точную копию оригинала.Statistics: Posted by begoon — 22 Apr 2026 15:26

--------------------------------------------------------------------------------

Вебсайт и форумы • Re: На сайте нет httpS и это может стать проблемой

Пока нет...Statistics: Posted by Shaos — 22 Apr 2026 09:37